Often it can be very handy to have a CPU in an FPGA. Though some are sold with an integrated CPU, most are not. A popular option is to use a so called Softcore CPU, a CPU that is implemented in the FPGA’s logic. I decided to have a look at a few popular and some less popular ones to see how easy they are to use, how fast they are and which might be a good choice for a project.

The contenders

I have a few requirements any CPU must meet:

1. There must be a GCC or LLVM compiler available

2. No vendor specific CPU, a CPU should run on all FPGA’s

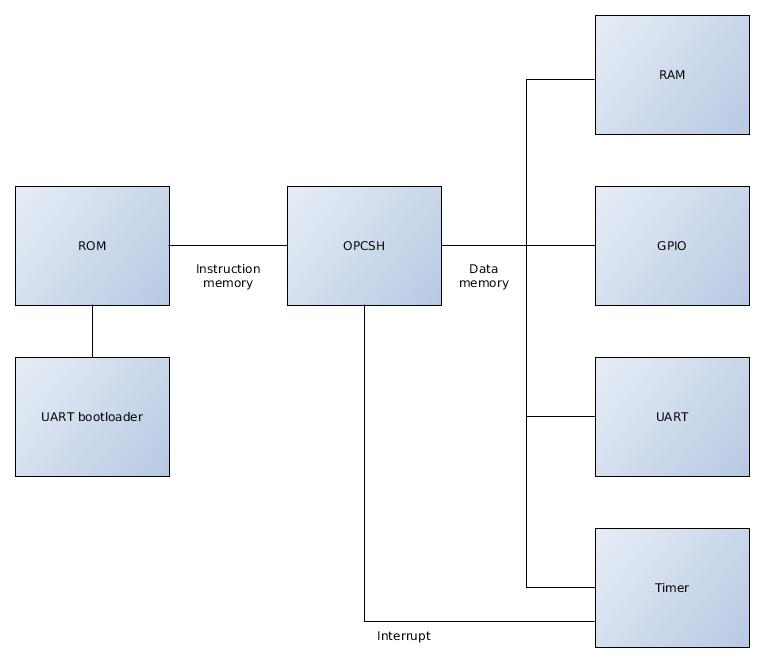

If possible, a simple ready to go SoC with Uart, Timer and GPIO is nice, but no requirement.

Not that many requirements, so after some googling I found the following options:

- VexRiscv

- LEON3

- PicoRV32

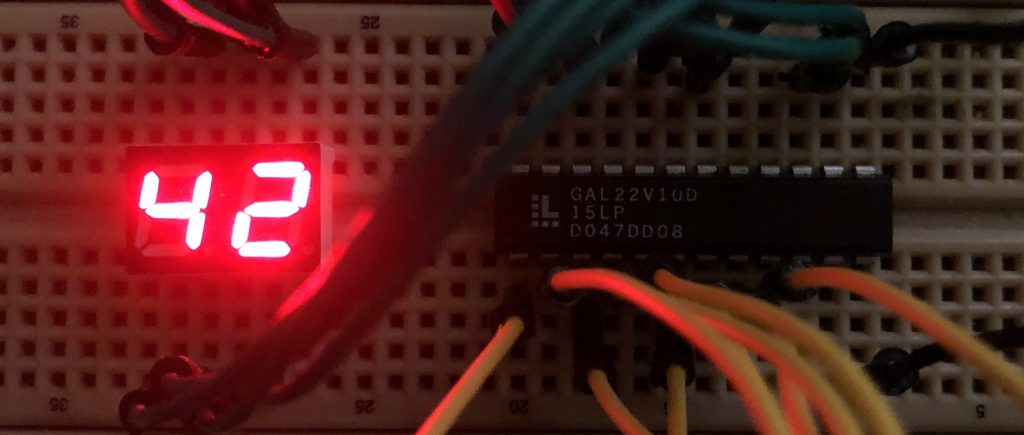

- Neo430

- ZPU

- Microwatt

- S1 Core

- Swerv EH1

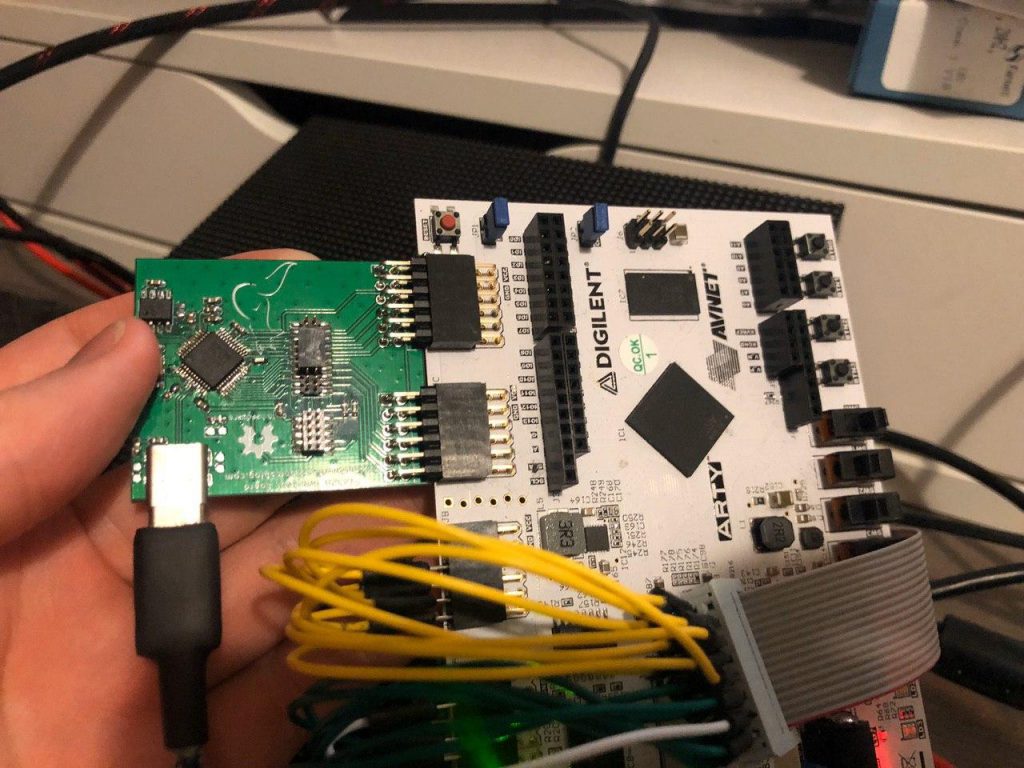

Sadly the S1 core and Swerv EH1 did not fit in my Arty board. I tried getting them small enough, but I need the Arty A7-100, so if anyone wants to sponsor me ;)

This still means 6 in total, and there are most likely some other good options as well that I missed.

From looking at the documentation, my gut feeling says that VexRiscv, LEON3 and Neo430 are going to be the nicest to use. I would say that the Microwatt, ZPU and the PicoRV32 are more hobby oriented. But let’s not get ahead of ourselves, each core will be looked at in more detail.

Continue Reading